東京都産業労働局「未来を拓くイノベーションTOKYOプロジェクト」 令和3年度採択案件

# 「革新的AIエッジデバイスを実現する CIM技術の開発」

第2回評価書【概要版】

令和5年6月

## はじめに

#### (1) 本事業の背景・課題

- 既存のAI技術は、クラウドにある大規模サーバーで膨大 な積和演算を繰り返すために、膨大な電力を消費します。

- また、自動運転などリアルタイム性が必要なアプリケーションでは、通信遅延やセキュリティの面の懸念から、サーバーを活用したAI演算には不向きな面があります。

- そのため、サーバーを介さず、エッジデバイス(※)内部で Al演算を行う必要性が高まっています。

- (※)エッジデバイス: AIやネットワークサービスを利用する際の、現場にある装置。

- エッジデバイスでは、サイズや電力供給量が限られるため、Al演算を行う半導体の小型・低消費電力化が求められています。

#### (2) 本事業で開発する技術・サービス

- メモリを使ってAIに必要な積和演算を行うCIM(Computing in Memory)の技術を用いて、エッジデバイスでAI 演算を行うのに最適な半導体デバイスを開発に取り組みます。

- 既存技術に比べて低消費電力で、複雑なAI演算を可能とすることを目指します。

### (3) 本事業により期待される波及効果

- ネットワークを介したデータのやり取りなしに、より高速で、高セキュリティで、筐体も小さく、低消費電力なAl演算が可能となり、様々なエッジデバイス(自動車、スマートフォン、PC、ドローン、ロボット、監視カメラ、スマートスピーカー、センサー・IoT機器等)におけるAl活用が普及すると見込まれます。

- AI活用を通じ、生活の様々なシーンや、労働現場(例:農業や介護等)の負荷軽減や効率化が期待されます。

CIM (Computing in Memory)について

#### 既存の Al

- エッジデバイスが状況を認識し、ネットワーク経由で 状況をサーバーに伝える。

- サーバーにあるAIが対応策を判断し、ネットワーク経由で、エッジデバイスに指示を与える。

- ・ エッジデバイスは指示に従い、行動する。

### 本事業

- エッジデバイスが状況を認識し、エッジデバイス内部のAIが対応策を判断し、エッジデバイスが行動する。

- ※サーバーを介さないため、通信遅延やセキュリティ の懸念が少ない

# 本事業の概要

| 事業者名       | 株式会社フローディア               |

|------------|--------------------------|

| 都内所在地      | 東京都小平市小川東町1-30-9 マルメゾン2F |

| 代表者名       | 代表取締役社長 奥山 幸祐            |

| 本事業の統括責任者  | 木之下 泰弘(取締役 CTO)          |

| 本事業の実施期間   | 令和4年4月~令和6年3月            |

| プロジェクトメンバー | 丸紅ベンチャーズ株式会社             |

## 本事業の実施内容

本事業では、これまでの研究開発実績(シミュレーションソフト上でのCIM技術を高度化する等)を活用し、ビジネス化に向けた取り組みを進めていく。

まず、これまで開発してきたCIM技術を搭載した半導体デバイスを設計し、ファウンドリ(半導体性製造を行う工場)に試作製造を依頼する。

試作品の評価に必要なツール等を整えつつ、実際に評価を実施し、CIM技術に関連したソフト・ハードの開発を深め、実用化(デモ制作、商用化)に向けた準備を進めていく。

#### 本事業の主要プロセス

| 時期    | 主要な実施事項                                                                  |  |

|-------|--------------------------------------------------------------------------|--|

| 令和4年~ | ・ ファウンドリによる試作実施 本事業における                                                  |  |

| 令和5年~ | ・ 各種技術の検証・強化<br>・ 量産化に向けた改良 支援期間<br>(~令和5年度末)                            |  |

| 令和6年~ | <ul><li>・ 半導体メーカーでデバイスが製造可能な体制整備</li><li>・ 関連したインターフェイス・ソフトの開発</li></ul> |  |

世界のAIに関連した半導体メーカー、ソフトウェアメーカーに対して、 デモを見せられるようにしていく

## 本事業終了時点(令和5年度)の達成目標①

# メモリセルを CIM動作させるための 機能と性能の実現

- ・ AI(人工知能)の演算に適したメモリセルを設計する。

- ・特に、アナログ書き込みへの対応を実現する。

- ・高品質で、長時間の稼働が可能なものとする。

- (※)・メモリセル:半導体メモリにおいて、最小単位となる回路構成のこと

- ・CIM: Computing In Memoryの略。AI(人工知能)に必要な演算をメモリの読出し動作で実行する方式。

- ・アナログ書き込み:デジタル書き込みでは、Oor1のデータを扱う。一方、アナログ書き込みでは、連続的・複数のデータを扱うことができる。

## ■標2

CIMコアテストチップの 機能動作と性能の実現

FP-CIMテストチップの 機能動作と性能の実現

- ・設計に基づき、実際に試作品を製造し、想定した動作が行われるか、性能が実現されるかについて確認する。

- ・コアテストチップ(特定の半導体メモリ)における動作・性能につき、 使用者が調整できるプログラム機能を実装する。

- ・コアテストチップとして、優れた電力効率を実現する。

- ・設計に基づき、実際に試作品を製造し、想定した動作が行われるか、性能が実現されるかについて確認する。

- ・ FP-CIMテストチップ(複数の半導体メモリを組合せたもの)における動作・性能につき、使用者が調整できるプログラム機能を実装する。

- ・ FP-CIMテストチップとして、優れた電力効率を実現する。

(※)・FP-CIM: Field Programmable-Computing In Memoryの略。AIに必要な演算の構成を設計者がフィールド(現場)でプログラムできる機能をもったCIM・フィールドプログラム機能: 設計者がフィールド(現場)で論理回路の構成をプログラムできる機能。目標②③にて、実装を実現する。

## 本事業終了時点(令和5年度)の達成目標②

● 機能面・性能面につき、具体的には下記目標を設定する。

メモリセルを CIM動作させるための 機能と性能の実現

# € 目標②

CIMコアテストチップの 機能動作と性能の実現

FP-CIMテストチップの 機能動作と性能の実現 ・機能面: -アナログ書き込みを可能とする機能

-CIM読出し機能

・性能面: -書込み精度:32レベル以上

-推論動作維持時間:1000時間以上

・機能面 -アナログ書き込みを可能とする機能

-CIM読出し機能

-コア内動作のフィールドプログラム機能

・性能面: -ビット書き込み精度:32レベル以上

-推論動作時間:1000時間以上

-CIMの処理能力:200TOPS/W以上

・機能面: -複数コアの連結動作

-複数コア間のフィールドプログラム機能

・性能面: -チップの演算処理能力:20TOPS/W以上

- (※)・書込み精度:特定のアナログ入力に対して、実際にメモリに書込むことのできる値の分解能。

- ・書込み精度:32レベル=メモリに32レベルの値を書込むことが可能。現状、この分解能を実際の半導体メモリで実現できれば、高性能と見なせる水準。

- ・TOPS/W:Tera Operation Per Second/Wattの略。消費電力1Wあたりの処理速度で、数値が大きいほど、電力効率が良いことを意味する。

1TOPS/Wは、1W当たり1秒に1兆回(Tera=10の12乗)の処理能力であることを示す。

CIMとして200TOPS/W、チップとして20TPOS/Wの水準は、現時点において業界最高峰と見なせる水準。

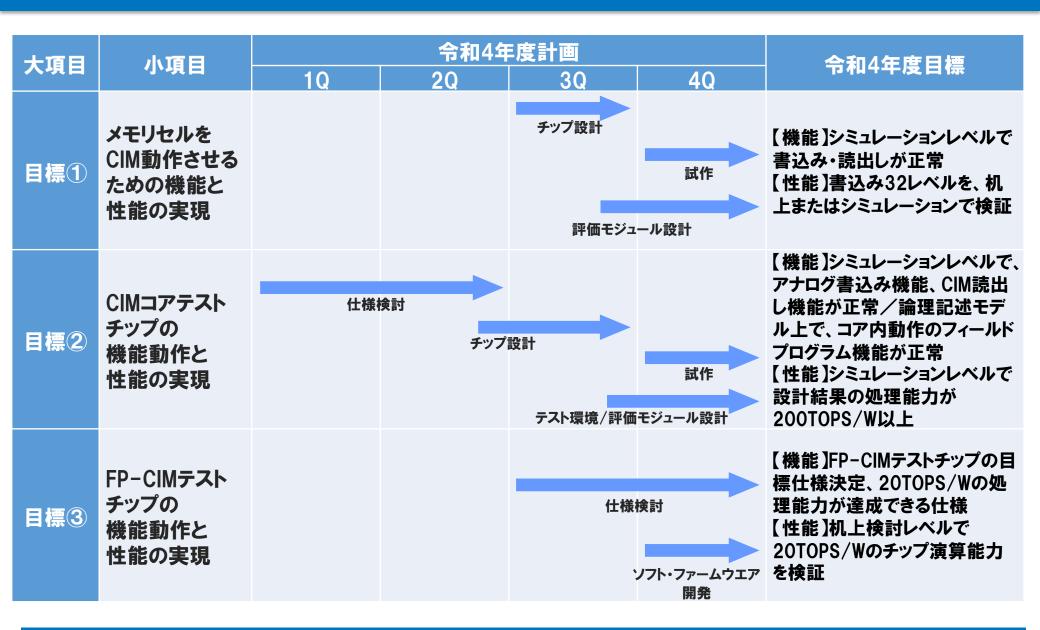

## 令和4年度の実施計画

# 令和4年度下期 取組状況と成果①

### (1)達成目標に関する取組と成果

| 大項  | 小項目                                   | 令和4年度下期目標                                                                                                   | 令和4年度下期の取組と成果                                                                                                                                                                                                                         | 評価 |

|-----|---------------------------------------|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 目標( | メモリセルを<br>CIM動作させる<br>ための機能と<br>性能の実現 | 【機能】シミュレーションレベルで書込み・読出しが正常<br>【性能】書込み32レベルがセンスでき<br>出力できる回路方式であることを、机<br>上またはシミュレーションで検証                    | <ul> <li>・ シミュレーション上、書込み・読出し<br/>に問題がないことを確認した。</li> <li>・ 机上にて、回路設計結果と過去の<br/>研究成果の活用により、書込み32<br/>レベルを実現できることを確認した。</li> </ul>                                                                                                      | 0  |

| 目標( | CIMコアテスト<br>チップの<br>機能動作と<br>性能の実現    | 【機能】シミュレーションレベルで、アナログ書込み機能、CIM読出し機能が正常/論理記述モデル上で、コア内動作のフィールドプログラム機能が正常【性能】シミュレーションレベルで設計結果の処理能力が200TOPS/W以上 | <ul> <li>CIMコアテストチップの基本設計、詳細設計を実施し、シミュレーション上、問題がないことを確認した。</li> <li>机上計算にて、CIMコアテストチップの処理能力が200TOPS/W以上であること確認した。</li> </ul>                                                                                                          | 0  |

| 目標( | FP-CIMテスト<br>チップの<br>機能動作と<br>性能の実現   | 【機能】FP-CIMテストチップの目標仕様決定、20TOPS/Wの処理能力が達成できる仕様<br>【性能】机上検討レベルで20TOPS/Wのチップ演算能力を検証                            | <ul> <li>FPの実現には、SRAM併用の必要があることが仕様上明らかになった。</li> <li>机上計算にて、FP-CIMテストチップの処理能力が20TOPS/Wを満たすことを確認した。</li> <li>※FP:Field Programmable、技術者が現場でプログラムできる機能</li> <li>※SRAM: Static Random Access Memory、一般に、小容量ながら、論理部品と混載しやすいメモリ</li> </ul> | 0  |

## 令和4年度下期 取組状況と成果①

### (1)達成目標に関する取組と成果

● 設計した回路につき、シミュレーションや机上検討を通じ、成果(目標の実現)を確認した。

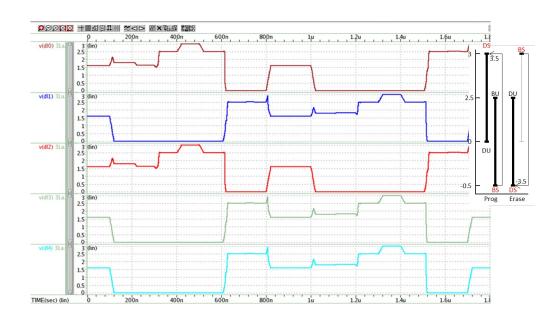

#### シミュレーションの実施

多様な電圧の出力が実現でき、 32レベルの書き込みが可能であることを確認。

### 机上検討の実施

3項 アレイ部電力計算

| BL部電力(2368 <sup>2</sup> ):0.5 x (2368 <sup>2</sup> x 0.1fF) x 0.8V <sup>2</sup> WL部電力(2368 <sup>2</sup> ):0.5 x (2368 <sup>2</sup> x 1.1fF) x 0.8V <sup>2</sup> | =0.18 nJ(AC)<br>=1.98 nJ(AC) |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| アンプ部電力(2368): 2368 x 0.7uA x 1.6V x 1uS                                                                                                                         | =2.65 nJ(DC)                 |

| 合計(アレイ動作サイクル=1MHz)                                                                                                                                              | =4.81 nJ                     |

| ·連続動作(1 MHz)                                                                                                                                                    |                              |

| BL部電力(2368 <sup>2</sup> ):0.5 x (2368 <sup>2</sup> x 0.1fF) x 0.8V <sup>2</sup> x 1MHz                                                                          | =0.18 mW(AC)                 |

| WL部電力(2368 <sup>2</sup> ):0.5 x (2368 <sup>2</sup> x 1.1fF) x 0.8V <sup>2</sup> x 1MHz                                                                          | =1.98 mW(AC)                 |

| アンプ部電力(2368): 2368 x 0.7uA x 1.6V                                                                                                                               | =2.65 mW(DC)                 |

| 合計(アレイ動作サイクル=1MHz)                                                                                                                                              | =4.81 mW                     |

| 処理性能                                                                                                                                                            |                              |

| ・1回当たり                                                                                                                                                          |                              |

| 2368 <sup>2</sup>                                                                                                                                               | =5.60 MegOpe                 |

| ·連続動作(1 MHz)                                                                                                                                                    |                              |

| 2368 <sup>2</sup> x 1MHz                                                                                                                                        | =5.60 TOPS                   |

| 電力効率                                                                                                                                                            | =1167 TOPS/W                 |

| ・以上より、200TOPS/Wを以上を達成する事を確認した。                                                                                                                                  |                              |

目標とする電力効率の実現が可能であることを確認。

# 令和4年度下期 取組状況と成果②

### (2) その他の主な取組と成果

| 取組内容                                            | 主な成果                                                                                  |

|-------------------------------------------------|---------------------------------------------------------------------------------------|

| 知的財産                                            | ・ 「CIM機能を3次元状に構成したメモリアレイにおいて実現するためのアレイ構成および<br>製造方法に関する特許」について、PCT(国際出願)、および、台湾出願を実施。 |

| マーケティング・<br>販路開拓、<br>事業会社との<br>オープンイノベーション<br>等 | 特になし                                                                                  |

## 令和5年度に向けた課題と対応策

#### 課題 試作に協力可能な工場の確保

- 半導体市場の好況が続いており、当初想定していた協力先工場の稼働が逼迫し、 予定していた試作品製造の依頼を行うことが難しいという事態が発生した。

- ・ 研究開発計画の見直し等を実施した上で、 新たな協力先にて、試作品製造を実施す ることができた。

- ・ ただし、各種調整等に時間を要したため、 試作品の完成が約2カ月遅延した。

#### 課題に対する対応策

・ 令和5年度の活動を通じ、遅延を吸収して スケジュール全体をキープするように努める ことで、最終的な目標達成に支障が生じな いようにする。

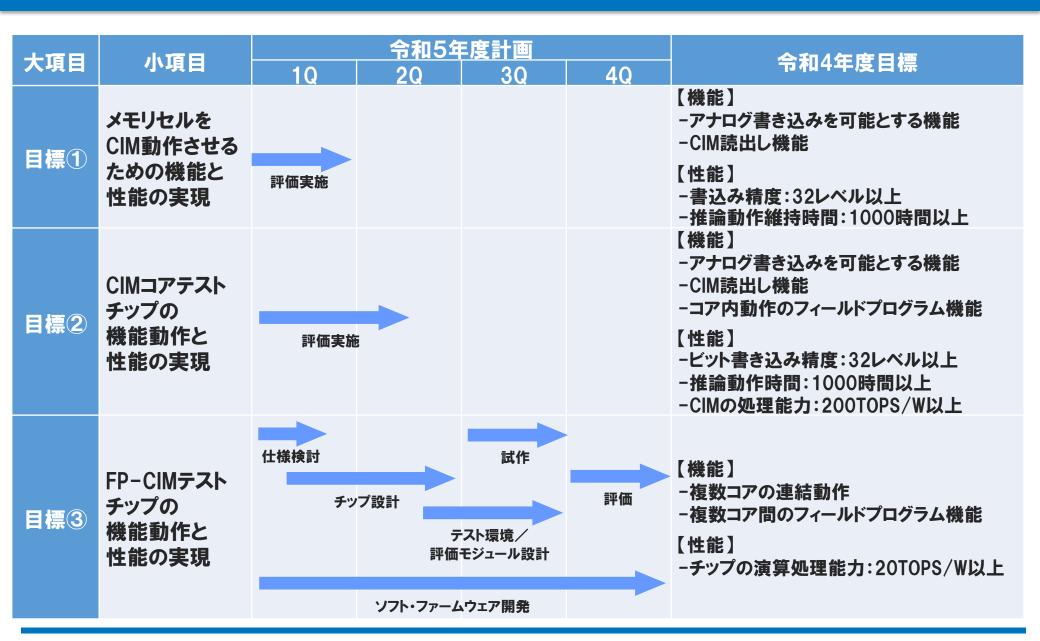

## 令和5年度の実施計画

## 令和4年度下期 事業評価

#### (1) 令和4年度下期目標の達成状況

● 令和4年度下期における目標は、達成済みであることが確認された。

#### (2) 今後の事業にあたって留意すべき事項

- 研究開発計画の着実な実行

- ・ 試作品の完成が約2カ月遅延したものの、令和5年度の活動を通じてスケジュール全体を維持する 見通しが立っていることは評価できる。

- ただし、更なる想定外のリスクが発生した際には、スケジュールを維持する余裕に乏しいと懸念される。

- ・ 本研究開発に関連した各機関とより一層の連携を行い、スケジュールの維持に努めることが重要である。

- 事業化を意識した関連取組の実行

- ・ マーケティング・販路開拓等の検討を深め、競合他社に対してどのような優位性を確立するかにつき、 より明確化されることが望ましい。

- 特に、本技術に適したアプリケーションが明確化されることは、顧客開拓等にも影響を与える重要事項であることから、アプリーケーションに関する検討を深め、対外的に発信していくことが重要である。